Lifetime Prediction for Electronics Funded by NSWC Crane Division

CIVS was awarded a DoD grant from the Naval Surface Warfare Center (NSWC) – Crane Division for the study of lifetime prediction in electronics components in Spring 2020. Using the combined efforts of experimental studies, statistical analysis, and numerical modeling, students examined the aging of a transistor under different environmental conditions. Supervised by Prof. Hansung Kim of Mechanical Engineering and Research Engineering Nick Walla of CIVS, students Emily Higley and Konstantinos Triantafyllou worked throughout the summer to capture the physical and electronic behaviors of transistors exposed to a variety of temperatures, humidity levels, and even the presence of chemical effects. This was the second grant awarded by NSWC Crane to CIVS as a study of aging in electronic components, with the previous work occurring in 2018-2019.

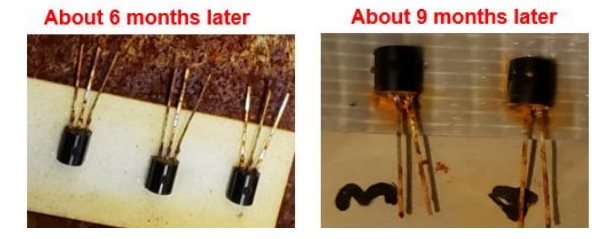

Life prediction of equipment using simulation and visualization is often applied to mechanical components, exploring the fatigue that builds as equipment goes through use cycles under various loads. In a similar fashion, this work applies the same concepts of degradation to electronic components, specially transistors. Through the use of static aging chambers—temperature controlled environments that can be used to statistically model long-term effects in a short-term study—student Konstantinos Triantafyllou and Professor Hansung Kim studied the length of time before common BJT transistors failed under different temperature and environmental conditions (such as the presence of epoxy outgassing). Using statistical and analytical modeling, the experimental team were able to apply their results to predict failure time for a variety of conditions, even those not directly tested.

The simulation team of student Emily Higley and CIVS Research Engineer Nick Walla then used a 3D simulation model of the transistor and applied the same aging conditions. Adding in a humidity-based corrosion model, a visualization was created of transistor performance decay over time. The methodology developed can be applied to a variety of components, whether electrical or mechanical. Plans for continued development of this methodology include additional considerations for material degradation due to corrosion, the coupling of the model with mechanical failures, and multi-scale modeling where small scale (like the single transistor) results can be included in larger-scale models, such as the simulation of an entire circuit assembly.